Royg Biv – Kapasitansi adalah kemampuan suatu komponen atau rangkaian untuk mengumpulkan dan menyimpan energi dalam bentuk muatan listrik. Komponen elektronika yang dapat menyimpan muatan listrik antara lain kapasitor dan baterai. Perbedaannya adalah apakah kapasitor melepaskan daya dengan cepat, tetapi baterai secara bertahap. Kapasitor terdiri dari dua konduktor yang dipisahkan oleh bahan dielektrik (isolasi).

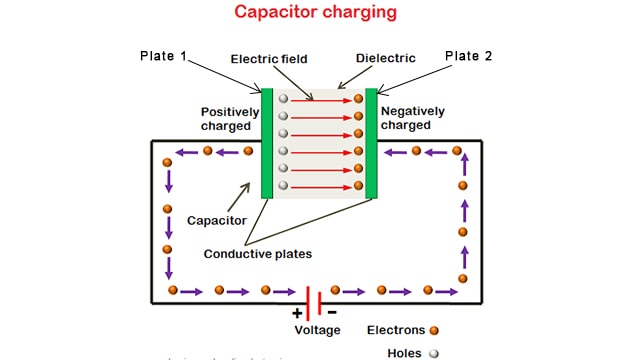

Kapasitor terdiri dari dua bahan konduktif yang mengapit isolator, ketika salah satu pelat konduktif diberi energi oleh sumber daya, seperti baterai. Pelat penghantar kapasitor 2 yang menerima polaritas negatif baterai akan kelebihan elektron sehingga menginisiasi konduksi pada pelat 1, mengalirkan elektron dari pelat 1 ke polaritas positif baterai.

Dengan cara ini, pelat 2 kapasitor yang kelebihan elektron akan bermuatan negatif dan pelat 1 yang kekurangan elektron akan bermuatan positif. Muatan pada kapasitor akan berkurang/habis jika diberikan muatan pada kapasitor. Kapasitansi kapasitor kecil, tetapi dapat ditingkatkan dengan cara berikut:

- Pelat konduktif kapasitor ditempatkan bersama.

- Dengan menggunakan peta yang lebih besar, maka lebih banyak ruang untuk proses kapasitas.

- Gunakan bahan dielektrik (isolasi) terbaik sesuai kebutuhan.

Pengertian Kapasitansi Stray

Kapasitansi liar atau kapasitansi parasit adalah kapasitansi yang tidak diinginkan dalam suatu rangkaian. Jadi jika kapasitansi kapasitor diinginkan, Anda memerlukan komponen ini. Namun, masalahnya di sini adalah kapasitansi parasit atau yang tidak diinginkan dihasilkan.

Kapasitansi parasit terjadi ketika dua permukaan dengan potensial listrik yang berbeda, dan yang cukup dekat untuk menghasilkan medan listrik, memiliki kapasitansi dan karenanya bertindak sebagai kapasitor.

Kehilangan kapasitansi biasanya terjadi di sirkuit. Misalnya seperti kapasitansi parasit yang terjadi pada PCB. Kapasitansi parasit terjadi sebagai akibat dari pembentukan kapasitor virtual antara dua jalur yang dipisahkan oleh dielektrik. Dengan demikian, ini mengkompensasi perbedaan potensial yang dihasilkan saat arus listrik mengalir sangat dekat dengan jalur PCB. Nyatanya, efek stray capacitance sangat mungkin terjadi, bahkan untuk desain PCB terbaik pun masih mungkin terjadi. Karena sangat sulit untuk membuat yang sempurna.

Efek kapasitansi parasit dalam rangkaian perangkat tidak sepenuhnya diinginkan, karena dapat memengaruhi fungsionalitas perangkat. Misalnya seperti menimbulkan crosstalk, EMI (electromagnetic interference), dan masalah integritas sinyal.

Cara Mengurangi Kapasitansi Stray

1. Tingkatkan ruang antar konduktor. Jika memungkinkan, berikan jarak yang lebih besar atau lebih jauh antara setiap garis atau kabel dalam tata letak sirkuit. Kapasitansi berbanding terbalik dengan jarak antar konduktor. Jarak atau jarak yang lebih besar antara garis akan mengurangi kapasitansi liar dan juga mengurangi efek kopling silang.

2. Gunakan tanah dengan hati-hati. Pembumian direkomendasikan untuk mengurangi induktansi parasit, EMI, dan pembuangan panas. Namun, perhatikan bahwa tanah juga dapat meningkatkan kapasitansi parasit. Maka dari itu, pertimbangkan terlebih dahulu kelebihan dan kekurangannya agar Anda bisa menerapkannya dengan benar dan sesuai.

3. Hindari penggunaan jalan yang berlebihan. Vias diperlukan untuk menghubungkan beberapa lapisan PCB, tetapi penggunaan yang berlebihan dapat meningkatkan kapasitansi.

4. Gunakan bahan dielektrik dengan permitivitas rendah. Bahan dielektrik dengan permitivitas yang lebih tinggi menghasilkan kapasitansi parasit yang lebih besar, sedangkan permitivitas yang lebih rendah menghasilkan kapasitansi parasit yang lebih kecil.

Sumber: